前言

今天在读论文的时候,发现这篇论文的Introduction部分关于SSD架构总结的非常详细,于是就把原文相关部分翻译到这里,再补充一下对部分内容的解释以进行记录。

原论文:REIS: A High-Performance and Energy-Efficient Retrieval System with In-Storage Processing

正文

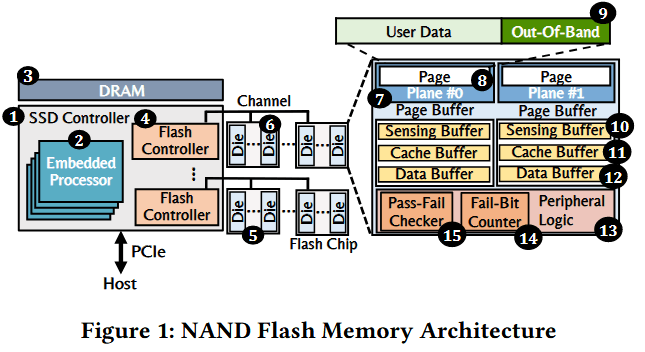

图 1 展示了基于 NAND 闪存的现代 SSD 架构概览。SSD 由 SSD 控制器、DRAM 和多个 NAND 闪存芯片组成。

SSD 控制器(图中:1) 负责处理来自主机的 I/O 请求,并执行垃圾回收、损耗均衡等维护任务。

SSD 控制器内置多个嵌入式微处理器(图中:2),这些处理器运行名为闪存转换层(FTL) 的固件。

SSD 控制器将元数据和频繁访问的页面存储在 SSD 内部的 DRAM(图中:3) 中,DRAM 容量通常为存储容量的 0.1%(例如,每 1TB 存储容量配备 1GB DRAM)。

SSD 控制器会将每个 I/O 请求的逻辑页地址转换为物理页地址,并通过闪存控制器(图中:4) 向闪存芯片下发命令。

SSD 包含多个闪存控制器,它们是连接 SSD 控制器与闪存芯片(图中:5) 的嵌入式处理器,每个闪存控制器负责与共享同一通道的多个闪存芯片通信,选择读写操作的目标闪存芯片并启动命令与数据传输。

每个 NAND 闪存芯片由多个Die(图中:6) 组成,这些Die可独立运行。每个Die包含 2-16 个平面Plane(图中:7),平面可并行执行读写操作。平面进一步划分为多个块组,每个块包含数百个页面Page(图中:8) 。

闪存页面的典型大小为 16KB,由数千个水平排列的 NAND 闪存单元构成,主要存储用户数据,且包含一个专用的带外区域(OOB 区域,图中:9)(例如 64-256 字节),用于存储纠错码相关元数据及逻辑 - 物理地址映射信息。

NAND 闪存以页面为粒度执行读取和编程操作,以块为粒度执行擦除操作。每个Die配备一个页缓冲器,作为读写操作的中间缓冲,该缓冲器包含多个子缓冲(例如,每个闪存单元存储 3 位时配备 3 个缓冲),用于暂存闪存页面的比特数据。传感缓冲器(图中:10) 是读取操作中临时存储闪存页面数据的主缓冲;缓存缓冲器(图中:11) 通过并行执行 “闪存芯片到闪存控制器的数据传输” 与 “下一次读取操作”,提升读取性能;数据缓冲器(图中:12) 主要用于两种场景:(1)向每个单元编程多个比特时;(2)从存储多个比特的闪存单元中读取单个比特时。

页缓冲器是 NAND 闪存裸片(Die)内部的专用临时存储组件,核心作用是在 “闪存单元←→外部(闪存控制器)” 之间做数据中转,解决闪存单元读写速度慢、操作粒度固定的问题,相当于闪存裸片的 “内部临时工作台”。

NAND 闪存的最小读写操作粒度是 “页面”(通常 16KB),但闪存单元的物理读写速度远慢于外部接口速度(比如闪存单元读一个页面要 50μs,而闪存控制器的通道带宽是 1GB/s)。页缓冲器的存在,就是把 “慢速度的闪存单元操作” 和 “高速度的外部数据传输” 隔离开:

页缓冲器不是单一的 “一块内存”,而是由多个子缓冲组成,不同子缓冲负责不同场景:

1.传感缓冲器:是页缓冲器的 “主存储区”,读取操作时,先把闪存单元里的页面数据读取到这里临时存储,再传输给闪存控制器。例子:读一个 16KB 的页面,先从闪存单元把数据 “搬” 到传感缓冲器,再从这里通过通道传给控制器。

2.缓存缓冲器:负责 “并行提速”:在当前页面的数据从传感缓冲器传给控制器的同时,下一个页面的数据可以提前读到缓存缓冲器里,避免等待,直接提升连续读取的性能。例子:读第 1 页时,第 2 页的数据已经预读到缓存缓冲器,第 1 页传完后直接传第 2 页,节省了 “再去读闪存单元” 的时间。

3.数据缓冲器:场景 1:给 TLC(3 位 / 单元)编程时,需要把 3 位数据拆分成不同子缓冲分别处理;第一步:先写第 1 位(最低有效位),这部分数据会临时存在数据缓冲器的第 1 个子缓冲里;第二步:再写第 2 位(中间位),数据存到第 2 个子缓冲;第三步:最后写第 3 位(最高有效位),数据存到第 3 个子缓冲;等 3 个子缓冲都填好数据,页缓冲器会把这 3 位数据 “合并” 后,一次性编程到同一个闪存单元里;数据缓冲器在这里的作用是:临时存储多比特数据的 “分步骤中间结果”,确保最终合并后写入的准确性。场景2:从 TLC 里只读取其中 1 位时,用这个缓冲器临时存储其他位的数据,避免干扰。第一步:先把这个单元的 3 位完整数据读到数据缓冲器里,第二步:数据缓冲器会把这 3 位数据 “拆分” 到不同子缓冲,只把需要的那 1 位数据提取出来,第三步:只将这 1 位数据传到传感缓冲器,再发给外部控制器。数据缓冲器在这里的作用是:先完整读取多比特数据,再拆分出目标比特,避免读取不必要的数据浪费带宽 。

根据每个闪存单元存储的比特数,可将其分为单级单元(SLC,存储 1 位)、多级单元(MLC,存储 2 位)、三级单元(TLC,存储 3 位)或四级单元(QLC,存储 4 位)。随着每个单元存储比特数的增加,SSD 容量会相应提升,但存储密度的提高会导致延迟增加、耐久性下降。为实现对闪存单元的可靠编程,SSD 厂商采用增量步长脉冲 / 擦除编程(ISPP/ISPE)技术,该技术通过多步迭代,逐步向闪存单元注入或抽出电子,直至达到目标电荷水平。每个闪存裸片的外围电路(图中:13) 包含片上数字比特计数器、通过 / 失败检测逻辑以及锁存器间的异或(XOR)逻辑;数字比特计数器与通过 / 失败检测逻辑用于检测单元状态并指导 ISPP/ISPE 编程过程,锁存器间的异或逻辑则通过片上数据随机化提升可靠性。